Schaltwerke in der Digitaltechnik

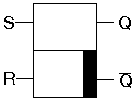

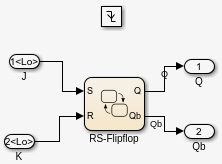

- RS-Flipflop:

- grundlegender Speicherbaustein

- Funktion

- S = 1 → 1 wird gespeichert → Q = 1, Qb

= 0

- R = 1 → 0 wird gespeichert → Q = 0, Qb

= 1

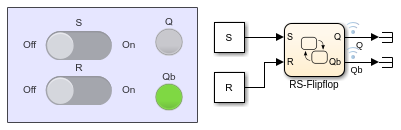

- als Zustandsautomat

- ausprobieren mit interaktiven Ein-/Ausgabe-Elementen

(Dashboard-Bibliothek)

- R = S = 1 → schaltet hinundher mit jedem

Solvertakt

- Tipp zur Benutzung von Dashboard-Eingabe-Elementen

- Verbindungsvariable in

Modell InitFcn definieren

(S = 0)

- Variablenname S

im Constant-Block eingeben

- im

Dashboard-Block Constant-Block anklicken

→ Variable S auswählen

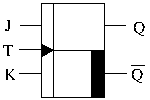

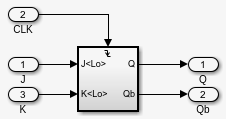

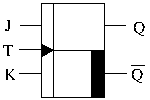

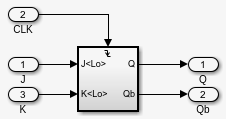

- Getriggertes JK-Flipflop:

- Problem: Laufzeiten von Signalen beim Umschalten

- Lösung: Taktgeber zur Synchronisierung

- Änderungen nur bei Wechsel am Takteingang

- bei steigender Taktflanke = bei Wechsel von 0 auf

1 (positiv getriggert)

- bei fallender Taktflanke = bei Wechsel von 1 auf

0 (negativ getriggert)

- hier immer negativ getriggert

- 3 Eingänge

- Takteingang T, J (≙ S), K (≙ R)

- J = K = 1 → Wechsel des Ausgangs mit jedem

Takt

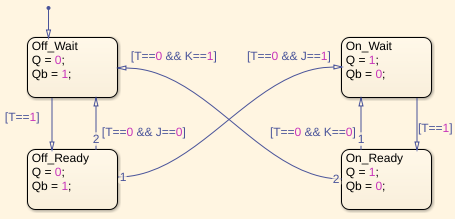

- als Zustandsautomat

- ausprobieren mit interaktiven Ein-/Ausgabe-Elementen

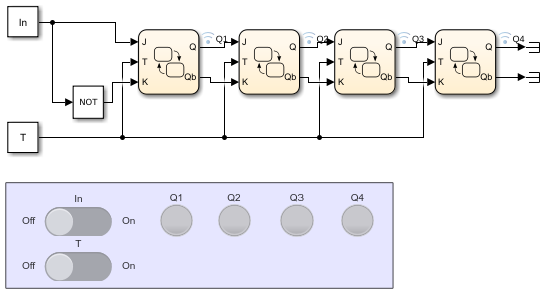

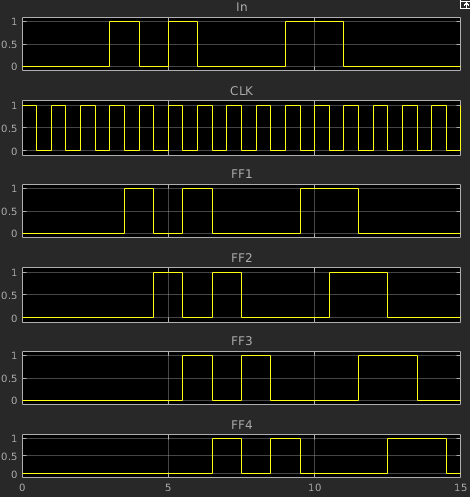

- Anwendung Schieberegister:

- Kette von Flipflops

- übergibt bei Taktimpuls Signal an das

nächste Flipflop

- Wandler zwischen seriellen und parallelen Signalen

- Modell schieberegisterA

- Problem

- Signal läuft bei einem Taktwechsel durch

- Ursache: "Gleichzeitigkeit der Signale" bzw.

"direct feedthrough"

- Getriggertes System in Simulink:

- enthält den Trigger-Block

aus der Ports & Subsystems-Bibliothek

- wird nur bei Auslösen des Triggers

ausgeführt, Ausgänge sonst konstant

- Trigger kann auf steigende oder fallende Flanke

(oder beides) reagieren

- Triggereingang ist oben (oder unten), nicht links

(oder rechts)

- Inport in getriggertem

Subsystem

- hat normalerweise aktuellen (neuen) Wert beim

Triggern

- muss hier alten Wert haben → Latch

input aktivieren

- Triggerung extra → intern genügt

RS-Flipflop

- Trick, um Takteingang an die Seite zu bekommen

- Flipflop in weiteres Subsystem verpacken

- Modell schieberegisterB

funktioniert

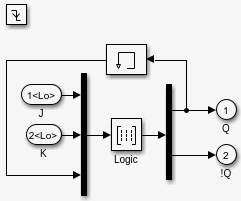

- Implementierung ohne Stateflow:

- RS-Flipflop schneller ohne Stateflow

- ersetze inneres Modell durch

- Logik-Block ersetzt komplexe logische Schaltung

- Wahrheitstabelle incl. Rückkopplung

-

| J |

K |

Qn |

Qn+1 |

!Qn+1 |

0

|

0

|

0

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

- Parameter Truth table = [0 1;

1 0; 0 1; 0 1; 1 0; 1 0; 1 0; 0 1]